[ad_1]

- El proveedor de portátiles modulares Framework dijo que lanzará un producto RISC-V en 2025

- RISC-V es el equivalente de hardware de Linux, es de código abierto y gratuito

- Más empresas de tecnología están adoptando esta tecnología, pero aún tiene que llegar a la corriente principal de manera significativa.

Riesgo-V, y Código abierto ISA fue desarrollado en la Universidad de California, Berkeley en 2010, y ha ganado constantemente interés como una alternativa personalizable a los estándares ISA propietarios, como x86 y brazo.

Su enfoque sin licencia permite a los fabricantes crear y modificar procesadores sin restricciones, lo que lleva a su adopción en muchas aplicaciones especializadas, y este año podría marcar un paso importante hacia una adopción más amplia de esta arquitectura por parte de los consumidores.

Para que RISC-V realmente llegue a la corriente principal, todavía necesita ganar terreno en el mercado de las computadoras portátiles. DeepComputing, con sede en Hong Kong, presentó su primera computadora portátil RISC-V, la Roma, en 2023, seguida de la DC-Roma II en 2024, que se envió con Ubuntu Linux preinstalado. Aunque elogiada por su flexibilidad de código abierto, el rendimiento de la computadora portátil quedó por detrás de las alternativas x86 y Arm, pero hablando con… Espectro IEEEYuning Liang, director ejecutivo de DeepComputing, dijo que el próximo dispositivo DC-Roma III de la compañía llenará este vacío con un rendimiento similar al Arm Cortex-A76.

Entra en el marco

Quizás lo más interesante es que DeepComputing se ha asociado con Framework, una empresa conocida por sus portátiles modulares y reparables, para crear una placa base RISC-V para el Framework Laptop 13. “Si miramos un par de generaciones hacia atrás, [software] Stack, estamos empezando a ver una línea de visión hacia RISC-V listo para el consumidor en algo como una computadora portátil o incluso un teléfono.

de acuerdo a Espectro IEEE“Aunque todavía está destinado a desarrolladores y primeros usuarios, será el portátil RISC-V más accesible hasta el momento y se entregará a los usuarios con la misma apariencia que los portátiles Framework que utilizan chips x86”.

el próximo Anuncio inicial En junio de 2024, el Marco A Página del producto Para una placa base RISC-V, pero sigue siendo un marcador de posición.

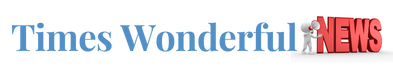

Sitio web de DeepComputing Sin embargo, revela más detalles, incluidas imágenes de la placa base DC-Roma RISC-V Framework 13 de la computadora portátil, una de las cuales puede ver en la parte superior de la página. La placa funciona con una CPU de cuatro núcleos RISC-V de 64 bits JH7110 y es compatible con Ubuntu Desktop 24.04 y Fedora 41.

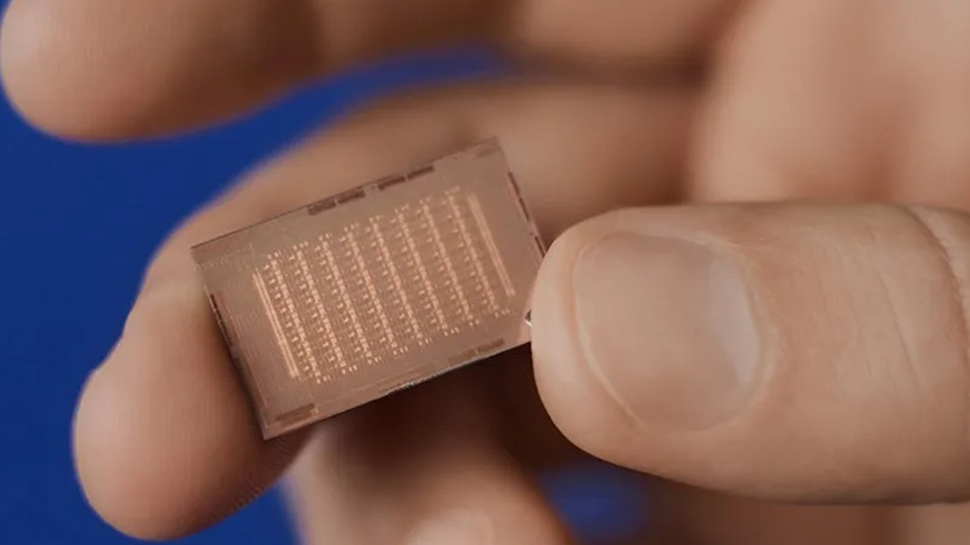

RISC-V ya ha sido adoptado por varias empresas de tecnología. Utilizado por Western Digital para controladores de almacenamiento, una startup británica Memoria de cambio azulEl procesador BlueFive de BlueFive se basa en el kernel RISC-V de código abierto Proyecto Xiangshan, China Desarrolló dos diseños, RISC-V y ubicación Tiene un procesador RISC-V de clase mundial que consolida todas las cargas de trabajo informáticas en un chip asequible.

Es probable que veamos más detalles sobre el portátil RISC-V 13 de Framework en los próximos meses, pero dado el enfoque actual en los desarrolladores y los primeros usuarios, junto con las limitaciones de rendimiento en comparación con arquitecturas establecidas como x86 y Arm, parece justo decir que aunque Este es sin duda un gran paso adelante para la arquitectura, ya que RISC-V aún no está listo para la adopción generalizada por parte del consumidor.

También te puede gustar

[ad_2]

Source Article Link