[ad_1]

- HBM es fundamental para la revolución de la IA porque permite una transferencia de datos ultrarrápida cerca de la GPU

- Escalar el rendimiento de HBM es difícil si cumple con los protocolos JEDEC

- Marvell y otros quieren desarrollar una arquitectura HBM personalizada para acelerar su desarrollo

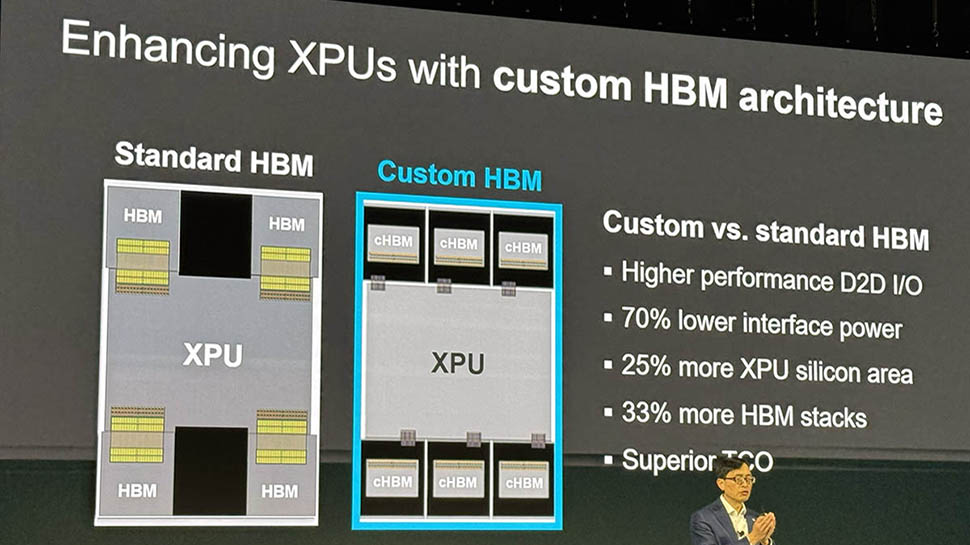

Marvell Technology ha presentado una arquitectura informática HBM personalizada diseñada para aumentar la eficiencia y el rendimiento de las XPU, un componente clave en el panorama de infraestructura de nube en rápida evolución.

La nueva arquitectura fue desarrollada en colaboración con los gigantes de la memoria Micron. Samsungy SK Hynix, para abordar las limitaciones en la integración de memoria tradicional proporcionando soluciones personalizadas para las necesidades de los centros de datos de próxima generación.

La arquitectura se centra en mejorar la forma en que las XPU, utilizadas en sistemas avanzados de inteligencia artificial y computación en la nube, manejan la memoria. Al optimizar las interfaces entre las matrices de silicio calculadas por IA y las pilas de memoria de gran ancho de banda, Marvell afirma que la tecnología reduce el consumo de energía hasta en un 70% en comparación con las implementaciones estándar de HBM.

Manténgase alejado de JEDEC

Además, se dice que su rediseño reduce los requisitos de espacio de silicio hasta en un 25 %, lo que permite a los operadores de la nube ampliar la capacidad informática o incluir más memoria. Potencialmente, esto permite que las XPU admitan hasta un 33% más de pilas HBM, lo que aumenta significativamente la densidad de la memoria.

“Los principales operadores de centros de datos en la nube han ampliado el alcance de la infraestructura dedicada. Aumentar las XPU con diseño de HBM para un rendimiento, potencia y costo total de propiedad específicos es el último paso en un nuevo paradigma para la forma en que se diseñan y entregan los aceleradores de IA”, dijo Marvell. Grupo de almacenamiento.

“Estamos muy agradecidos de trabajar con diseñadores de memoria líderes para acelerar esta revolución y ayudar a los operadores de centros de datos en la nube a continuar escalando sus XPU e infraestructura para la era de la IA”.

HBM desempeña un papel central en las XPU, que utilizan tecnología de empaquetado avanzada para combinar memoria y potencia de procesamiento. Sin embargo, las arquitecturas tradicionales limitan la escalabilidad y la eficiencia energética.

El nuevo enfoque de Marvell modifica e integra la propia pila de HBM, con el objetivo de ofrecer un mejor rendimiento con menor energía y menores costos, consideraciones clave para los hiperescaladores que buscan constantemente gestionar las crecientes demandas de energía en los centros de datos.

Servicio a domicilio's Patrick Kennedy, quien informó la noticia en vivo desde Marvell Analyst Day 2024, señaló que cHBM (custom HBM) no es una solución JEDEC y por lo tanto no será estándar en HBM.

“Alejar la memoria de los estándares JEDEC a una personalización a hiperescala es un gran paso para la industria”, escribe. “Esto demuestra que Marvell tiene grandes beneficios para las XPU de gran volumen, ya que este tipo de asignación de espacio de memoria no ocurre en pedidos pequeños”.

La colaboración con los principales fabricantes de memorias refleja una tendencia más amplia de la industria hacia un hardware altamente personalizado.

“Aumentar la capacidad de memoria y el ancho de banda ayudará a los operadores de la nube a escalar de manera eficiente su infraestructura para la era de la IA”, dijo Raj Narasimhan, vicepresidente senior y gerente general de la unidad de negocios de Computación y Redes de Micron.

“Las colaboraciones estratégicas centradas en la eficiencia energética, como la que tenemos con Marvell, se basarán en las especificaciones de energía HBM de Micron, líderes en la industria, y proporcionarán a los hiperescaladores una plataforma poderosa para ofrecer las capacidades y el rendimiento óptimo necesarios para escalar la IA”.

Más de TechRadar Pro

[ad_2]

Source Article Link