[ad_1]

Samsung Foundry and TSMC are the world’s most advanced contract chip manufacturers, and TSMC has had the upper hand over the past few years. While Samsung has been trying to up its game, it hasn’t succeeded. With its 3nm chip fabrication process, the South Korean firm had hoped to win back big-name clients, but even that didn’t happen. TSMC has made another move that widens its gap with Samsung.

TSMC unveils cheaper 4nm chips

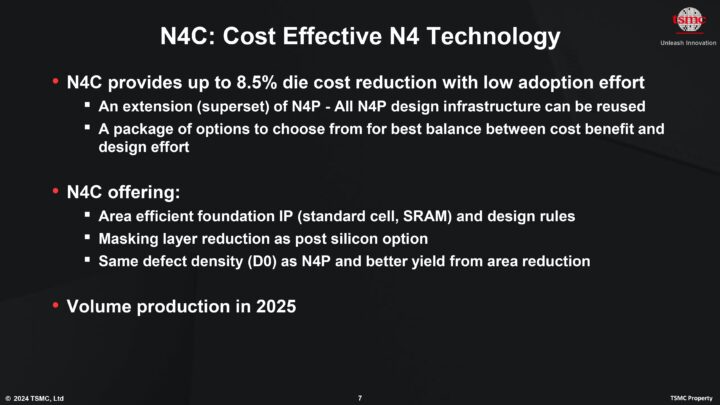

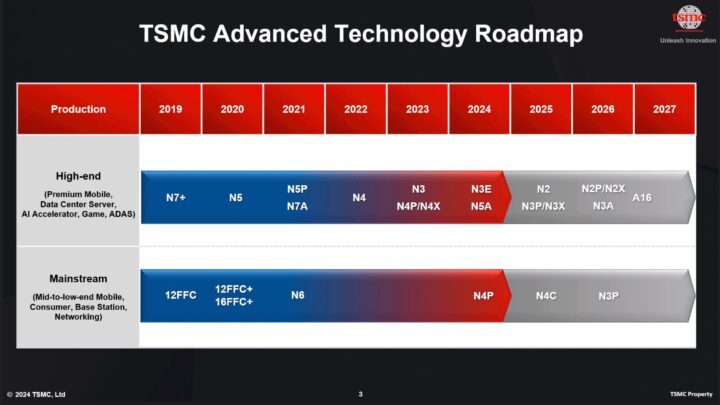

TSMC revealed its new chip fabrication node, N4C, at the North American Technology Symposium 2024. It is a cheaper tier of its 4nm process and superset of N4P, its most advanced technology in the 5nm class process. According to AnandTech, TSMC is modifying the architecture of the cell structure and SRAM, reducing the number of masking layers, and changing some other design elements to reduce the complexity of the chips. This will, in turn, reduce die size by 8.5% and fabrication complexity. It is also said to have a better yield than N4P.

The Taiwanese firm also offers several options for chip firms to focus on cost or design efforts. While big-name brands like Apple, AMD, MediaTek, Nvidia, and Qualcomm aim to use TSMC’s 3nm process for their flagship chips, many chip firms will likely use the N4C process for their non-flagship chips to reduce fabrication costs and create value-for-money chips. Chips based on N4C could be released sometime next year, and the process could be used for years to come.

In comparison, Samsung has recently released the Exynos 2400 chip based on its third-generation 4nm process. Its fourth and fifth-generation 4nm processes are expected to be ready later this year and in 2025. However, the company hasn’t promised any figures for their efficiency and performance.

TSMC promises to start mass production of 1.6nm chips in 2026

TSMC also unveiled its first Angstrom-class chip manufacturing process, A16 (1.6nm). It will be the first process to use Backside Power Delivery Network (BSPDN) technology for massive performance and power efficiency improvements. The BSPDN technology was promised to be used in TSMC’s 2nm process, but it has been removed from 2nm and will debut in 1.6nm chips.

A16 will also use Gate-All-Around Field-Effect Transistor (GAAFET) to increase transistor density. This technology has already been used in Samsung’s 3nm process, but we haven’t seen its results yet. No PC or smartphone chip made using Samsung Foundry’s 3nm process has been released yet.

TSMC is promising performance improvement of 8% to 10% at the same power and complexity as the N2P process. Chips using the A16 process can offer 15% to 20% improved power efficiency at the same frequency and transistor count. Regarding transistor density, TSMC claims A16 offers a 7% to 10% improvement.

[ad_2]

Source Article Link