[ad_1]

Synopsys ha anunciado que sus herramientas de flujo de diseño y propiedad intelectual (IP) están listas para su uso. Fundición Samsung Proceso de fabricación de 2 nm.

Samsung Anunciado recientemente Estará listo para la producción en masa de chips semiconductores de 2 nm el próximo año y el proceso se optimizará aún más en 2027.

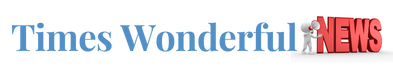

Las herramientas de diseño de Synopsys están certificadas para el proceso GAA de 2 nm de Samsung Foundry

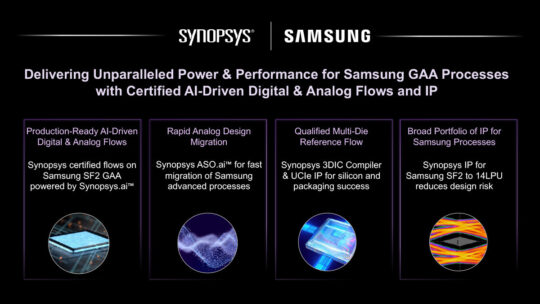

Las empresas de diseño de chips y los clientes interesados en fabricar sus chips utilizando el proceso de 2 nm de Samsung Foundry estarán encantados de saberlo. resumenLas herramientas de diseño analógico y digital basadas en IA han recibido la certificación para este nodo de proceso con múltiples casetes de chip.

Synopsys.ai es una suite completa de automatización de diseño electrónico (EDA) que mejora la migración de diseños analógicos, PPA y la productividad para Samsung Foundry. 2nm Puerta en todo el nodo de proceso (GAA). La solución de optimización de tecnología de diseño (DTCO) impulsada por AI-Sypsys optimizó el proceso de 2 nm de Samsung, mejorando el espacio, el rendimiento y la eficiencia energética.

Synopsys DSO.ai se utiliza para la productividad del diseño y la optimización de PPA, mientras que Synopsys ASO.ai se utiliza para una migración de diseños analógicos más rápida. Estos procesos se han implementado para la migración de diseños de FINFET a la arquitectura GAA, lo que significa que los clientes pueden migrar sus diseños de chips utilizados para el proceso FINFET de 8 NM (o heredado) al nuevo proceso GAA de 2 NM.

Las empresas de chips pueden utilizar las herramientas de Synopsys para desarrollar nuevas técnicas de diseño de chips, incluido el enrutamiento de energía inversa, la metodología de entrenamiento de impacto local y el diseño de nanocélulas, para mejorar la eficiencia y un mayor rendimiento con el proceso SF2. El nodo de procesamiento SF2Z de Samsung Foundry puede mejorar el rendimiento, la potencia y el área (en un 20%).

La historia continúa después del vídeo a continuación, que compara el rendimiento del Exynos 2400 con el del Snapdragon 8 Gen 3.

Se utilizó Synopsys UCIe IP para pelar chips mediante procesos SF2 y SF4x para lograr una integración más rápida de chips pequeños en paquetes de matrices múltiples. La latencia, la potencia y la conectividad directa también mejoran en el funcionamiento del SF5A. El compilador 3DIC para Synopsys se puede utilizar para integración heterogénea 2,5D y 3D y empaquetado avanzado.

Además, Synopsys reveló que la misma solución DTCO también se utilizará para optimizar el nodo de proceso de 1,4 nm (SF1.4) de Samsung Foundry.

[ad_2]

Source Article Link