Alphawave Semi and Keysight Technologies have joined forces to create a cutting-edge solution for the latest PCIe 6.0 standard. This collaboration is a response to the growing need for faster data transfer rates, which are becoming increasingly important for the operation of sophisticated AI and high-performance computing systems. The new PCIe 6.0 standard is set to dramatically increase data transfer speeds to 64 gigatransfers per second, a notable jump from the previous version.

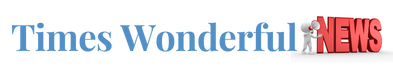

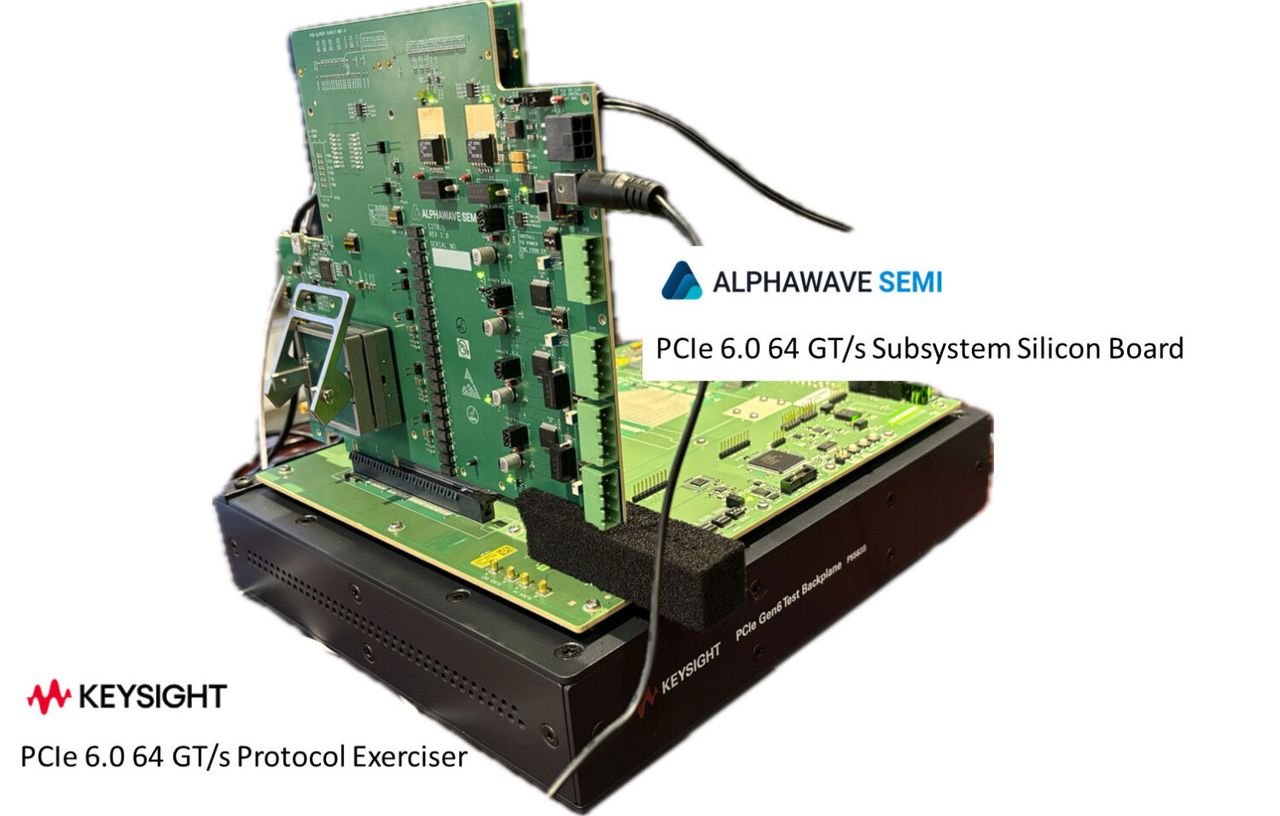

The partnership leverages Alphawave Semi’s expertise in PHY and Controller Device technology and Keysight’s Protocol Exerciser to achieve a significant breakthrough in data rate link negotiation. This is a crucial step for the implementation of PCIe 6.0. Alphawave Semi’s inclusion on the PCI-SIG 5.0 Integrators list emphasizes their dedication to adhering to rigorous industry standards, which is essential for the rapid adoption of the new technology.

One of the standout accomplishments of this collaboration is Alphawave Semi’s successful establishment of a CXL 2.0 link, which is a promising sign for future enhancements in data center efficiency. This is particularly relevant for the smooth operation of data centers, where cache coherency is a key factor.

PCIe 6

PCI Express (PCIe) 6.0 is the latest version of the PCI Express interface standard, which is widely used for high-speed data transfer in computers and servers. This version marks a significant advancement from its predecessor, PCIe 5.0, in several key areas:

- Data Transfer Speed: PCIe 6.0 doubles the data transfer rate of PCIe 5.0, reaching up to 64 gigatransfers per second (GT/s) per lane. This translates to raw data rates of around 128 gigabytes per second (GB/s) in a x16 configuration, commonly used for graphics cards and high-end storage devices.

- PAM4 Encoding: One of the most notable changes in PCIe 6.0 is the shift from Non-Return-to-Zero (NRZ) encoding to Pulse Amplitude Modulation with 4 levels (PAM4) signaling. PAM4 allows for more data to be transmitted with the same number of clock cycles by using four voltage levels instead of two, effectively doubling the bandwidth.

- Forward Error Correction (FEC): PCIe 6.0 introduces Forward Error Correction, a significant enhancement for data integrity. FEC can detect and correct errors within the data stream, improving the reliability of high-speed data transfers, which is crucial for maintaining data integrity at higher speeds.

- Low-Latency Flow Control Unit (FLIT): PCIe 6.0 uses a flow control unit called FLIT (Flow Control Unit-based encoding) to maintain low latency. FLIT-based encoding helps in managing the increased complexity of PAM4 signaling and FEC, ensuring that the latency doesn’t increase significantly despite the higher speeds and more complex encoding.

- Backward Compatibility: Like its predecessors, PCIe 6.0 maintains backward compatibility with previous generations of PCIe. This means that devices designed for PCIe 6.0 can still operate with PCIe 5.0, 4.0, etc., hardware, albeit at the lower performance levels of the older generation.

- Applications: The increased bandwidth and improved data integrity of PCIe 6.0 are particularly beneficial for applications that require high data throughput, such as data centers, artificial intelligence, machine learning, high-performance computing, and advanced networking systems.

PCIe 6.0 is an important development for future computing applications, offering significant improvements in speed and efficiency. Its adoption will likely be gradual, as it requires both hardware and software support to fully utilize its capabilities.

PCIe 6.0 Subsystem Solution

The role of test and measurement is crucial when introducing new technologies to ensure that products are interoperable and ready for widespread use. Keysight Technologies has pointed out the importance of PCIe in scaling AI and managing complex workloads. A significant technical shift in PCIe 6.0 is the move from NRZ signaling to Pulse Amplitude Modulation 4-level (PAM4). This change addresses challenges related to signal integrity and protocol, while also maintaining backward compatibility with previous PCIe generations. The introduction of Forward Error Correction (FEC) in FLIT-mode transactions is another key innovation, allowing PCIe 6.0 to handle higher bit error rates and ensure data integrity.

Alphawave Semi has showcased the effectiveness of FLIT-mode transactions on their PCIe 6.0 64 GT/s subsystem silicon, demonstrating the solution’s power efficiency, low latency, and reliability. Their PAM4 SerDes IP showcases their ability to provide leading-edge connectivity solutions.

Looking ahead, Alphawave Semi’s PCIe 6.0 Subsystem has the potential to support CXL 3.0, which could further enhance memory coherency in data centers and solidify the company’s position as a leader in high-speed connectivity for demanding computing environments. The joint efforts of Alphawave Semi and Keysight Technologies mark a pivotal step in the evolution of PCIe technology. This partnership is paving the way for a new era of high-speed connectivity that will be instrumental in driving forward the next generation of AI and high-performance computing developments.

Filed Under: Gadgets News

Latest timeswonderful Deals

Disclosure: Some of our articles include affiliate links. If you buy something through one of these links, timeswonderful may earn an affiliate commission. Learn about our Disclosure Policy.